揭秘:clk的真正含义是什么?

在日常的数字电路和计算机技术中,我们经常会遇到各种各样的缩写词,其中一个非常常见且重要的缩写就是clk。那么,clk的意思是什么呢?简单来说,clk是时钟(Clock)信号的缩写,它扮演着电子世界里指挥家的角色,确保电路中的所有元件都按照它的节奏来工作。下面,我们将从多个方面详细介绍clk的含义和作用。

clk的基本概念

首先,clk代表时钟信号,它是一种具有固定周期并与运行无关的信号量。这种信号是周期性的,不断变换状态,通常是上升沿和下降沿触发。在数字系统中,clk作为时钟信号,用于控制各个部件的操作节奏。例如,在计算机内部,clk信号会不断地发出高低电平变化,就像心脏的跳动一样,有规律地控制着各个组件的操作。

clk的作用与重要性

1. 同步操作:

clk信号的主要作用是同步各个组件的操作。在数字电路中,不同的元件需要按照固定的时间序列来执行操作,这样才能保证整个系统的正常运行。clk信号就像是一个统一的指挥棒,告诉每个元件何时该工作,何时该休息。这样,所有的操作都能在同一时间节奏下进行,避免了操作冲突和时序错误。

2. 状态更新:

时钟信号是时序逻辑的基础,它用于决定逻辑单元中的状态何时更新。在边沿触发机制中,只有上升沿或下降沿才是有效信号,才能控制逻辑单元状态量的改变。这种机制确保了状态变化的准确性和一致性。

3. 控制数据传输:

在数据传输过程中,clk信号也起到了关键的作用。它控制着数据的发送和接收,确保数据在正确的时间点被传输和处理。例如,在串行通信中,clk信号通常用于同步发送方和接收方的数据传输速率,确保数据能够准确无误地传输。

clk与时钟频率

除了表示时钟信号外,clk还可以代表时钟频率。时钟频率是指每秒的时钟周期数,通常用赫兹(Hz)来表示。例如,如果一个处理器的时钟频率为2.5GHz,意味着它每秒能进行约2.5亿次操作。时钟频率是评估计算机性能的一个重要指标,因为它直接影响处理器的运算速度。

高频率:高频率的clk信号可以让电路快速地工作,但也需要消耗更多的能量。就像乐团演奏激昂的乐曲需要更多的体力一样,高频率的处理器也需要更多的电力来支持其运行。

低频率:低频率的clk信号则可以让电路慢速地工作,但消耗的能量也比较少。这种设置在需要低功耗运行的场景中非常有用,如移动设备或嵌入式系统。

clk信号的边沿与触发机制

在数字电路中,clk信号的边沿(即上升沿和下降沿)是关键的触发点。这些瞬间决定了电路中的元件何时进行状态变化或执行特定的操作。

上升沿触发:当clk信号从低电平变为高电平时,会触发某些元件的操作。这种触发机制常用于同步计数器和状态机等电路中。

下降沿触发:同样地,当clk信号从高电平变为低电平时,也会触发某些元件的操作。这种触发机制在某些特定的应用场景中非常有用,如双稳态触发器。

clk信号的影响因素

就像指挥家指挥乐团会受到很多因素的影响一样,clk信号也会受到多种因素的影响:

1. 频率稳定性:clk信号的频率和相位需要准确稳定,这样才能保证电路的稳定性和可靠性。频率的波动会导致时序错误,影响电路的性能。

2. 抖动:clk信号的频率或相位可能会出现随机波动,这种现象称为抖动。抖动会影响电路的稳定性和时序精度,需要采取适当的措施来抑制。

3. 噪声:clk信号可能会受到外界噪声的干扰,这会导致信号质量的下降。为了提高信号的抗干扰能力,通常会采用差分信号传输或滤波等措施。

4. 时钟分配和传输:clk信号需要被准确地分配和传输到电路的各个部分。在大型系统中,时钟信号的分配和传输是一个复杂的问题,需要采用专门的时钟树设计来确保信号的均匀性和准确性。

clk信号的应用实例

clk信号在电子电路和数字系统中的应用非常广泛,以下是一些典型的应用实例:

1. 处理器时钟:在微处理器和微控制器中,clk信号是控制处理器执行指令的关键信号。处理器的时钟频率决定了其运算速度和性能。

2. 存储器时钟:在存储系统中,clk信号用于同步数据的读写操作。例如,在DRAM和SRAM中,clk信号会触发存储单元的状态变化和数据传输。

3. 通信接口时钟:在串行通信和并行通信接口中,clk信号用于同步数据的发送和接收。例如,在UART和SPI接口中,clk信号会控制数据的传输速率和时序。

4. 时钟发生器:在复杂的数字系统中,通常会使用专门的时钟发生器来产生多个不同频率和相位的clk信号。这些信号用于满足系统中不同组件的同步需求。

clk信号的未来发展

随着电子技术的不断发展,clk信号的设计和应用也在不断进步。例如,为了适应低功耗和高性能的需求,现代处理器通常采用动态电压和频率调节技术(DVFS),根据工作负载的变化实时调整clk信号的频率和电压。此外,随着5G、物联网和人工智能等技术的快速发展,对clk信号的精度、稳定性和灵活性提出了更高的要求。

总之,clk作为时钟信号或时钟频率的缩写,在电子电路和计算机技术中扮演着非常重要的角色。它确保了系统的同步运行和高效性能,是现代电子设备中不可或缺的一部分。通过深入了解clk信号的基本概念、作用与重要性、影响因素以及应用实例等方面的知识,我们可以更好地理解和应用这一技术,为电子技术的发展做出更大的贡献。

- 上一篇: 家常美味秘籍:轻松学会白菜豆腐汤的制作方法

- 下一篇: 轻松学会:如何查找网页上的单词

-

揭秘:SVIP的真正含义是什么?资讯攻略01-30

揭秘:SVIP的真正含义是什么?资讯攻略01-30 -

揭秘:Easter的真正含义是什么?资讯攻略01-18

揭秘:Easter的真正含义是什么?资讯攻略01-18 -

揭秘:“minutes”的真正含义是什么?资讯攻略11-01

揭秘:“minutes”的真正含义是什么?资讯攻略11-01 -

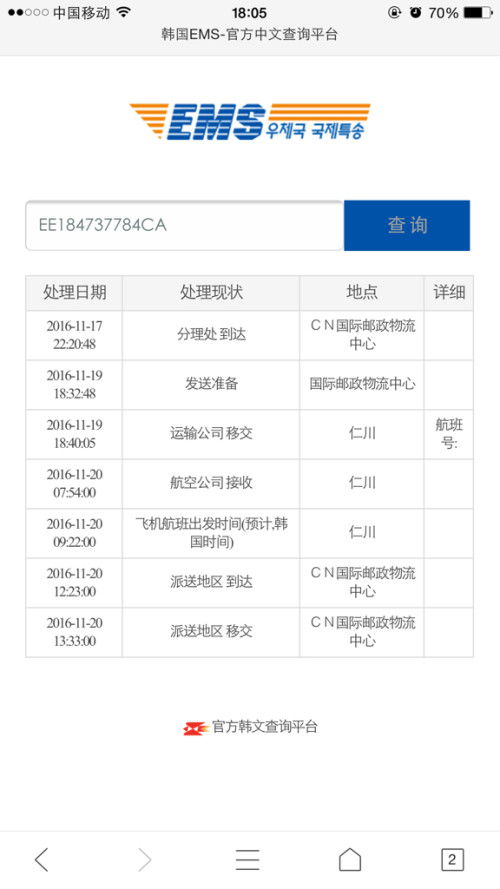

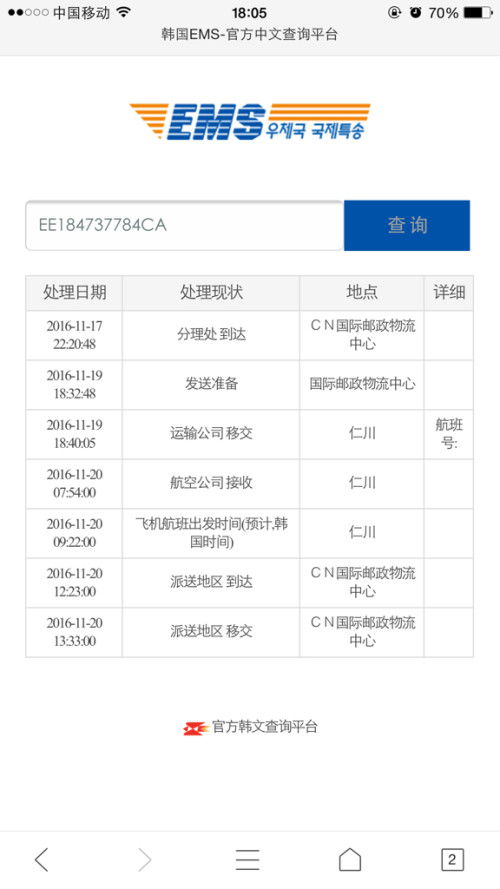

揭秘:EMS的真正含义是什么?资讯攻略11-18

揭秘:EMS的真正含义是什么?资讯攻略11-18 -

揭秘:“All of them”的真正含义是什么?资讯攻略02-21

揭秘:“All of them”的真正含义是什么?资讯攻略02-21 -

揭秘:Allroad的真正含义是什么?资讯攻略11-26

揭秘:Allroad的真正含义是什么?资讯攻略11-26